PMV0603-140E100电感值与共模电感协同设计的技术深度剖析

随着电子产品向微型化、高速化发展,对电磁兼容性(EMC)的要求日益严格。在这一背景下,如何合理搭配共模电感与高精度贴片电感如PMV0603-140E100,成为提升系统抗干扰能力的核心课题。本文将从电感参数、系统集成与仿真验证三个维度展开详细论述。

一、电感值匹配:为何100μH是理想选择?

1. 频率响应分析:PMV0603-140E100的100μH电感值在典型开关频率(如100kHz–1MHz)范围内,能够提供足够的感抗(XL=2πfL),从而有效阻碍共模电流流动。例如,在1MHz时,其感抗约为628Ω,远高于线路阻抗,形成良好衰减。

2. 与共模电感的串联配置:在滤波电路中,常将共模电感与PMV0603-140E100串联使用,构成多级滤波结构。这种“双电感”设计可显著提高整体插入损耗,尤其在中高频段表现优异。

二、共模电感与贴片电感的协同效应

1. 增强高频抑制能力:共模电感主要处理低频共模噪声(<100kHz),而PMV0603-140E100则在100kHz以上发挥主导作用,二者形成互补覆盖,实现全频段滤波。

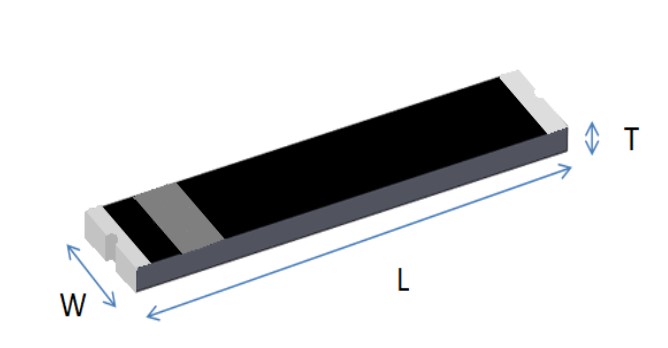

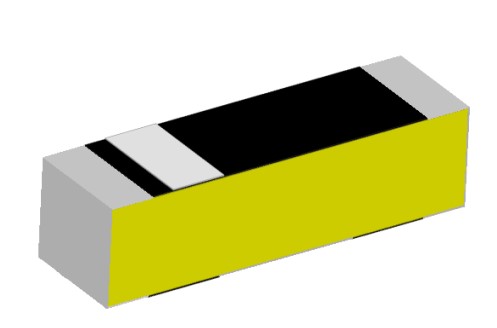

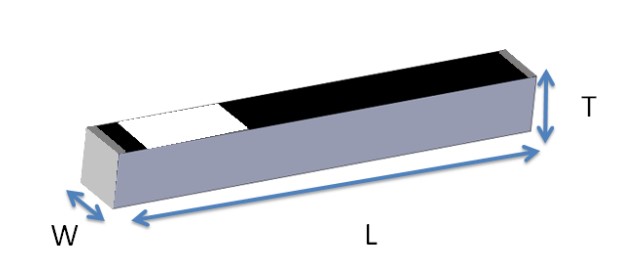

2. 减少寄生效应:由于PMV0603-140E100体积小、引脚短,可降低引线电感,避免高频下出现自谐振现象,提升滤波器的平坦度。

三、设计实践中的关键挑战与应对策略

- 自谐振频率(SRF)管理:PMV0603-140E100的自谐振频率约为12MHz,应在设计中避开此区域,避免电感呈现容性,反而放大噪声。

- 磁芯饱和问题:当共模电流超过电感额定值时,磁芯可能饱和,导致电感值骤降。建议设置冗余裕量,选用更高饱和电流的型号。

- PCB布局优化:建议将电感靠近电源入口端,且远离敏感模拟电路,减少噪声耦合路径。

四、仿真与实测验证方法

推荐使用LTspice、ADS或HFSS进行电路建模,建立包含寄生参数的完整模型。通过S参数仿真可预测滤波器在不同频率下的插入损耗曲线。实测阶段,应使用EMI接收机或频谱分析仪,按CISPR 22/32标准进行传导发射测试,并对比仿真结果进行调优。

五、未来发展趋势展望

随着5G、AIoT和电动汽车的发展,对滤波器件的小型化、高性能需求将持续增长。预计下一代贴片电感将采用新型纳米晶材料、多层叠绕结构,进一步提升电感密度与温度稳定性。而共模电感也将向集成式模块方向演进,实现“电感+滤波网络”的一体化封装。